### **General Description**

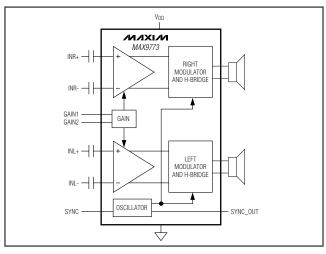

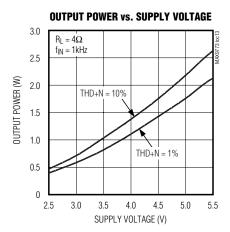

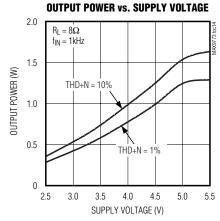

The MAX9773 3rd-generation, ultra-low EMI, stereo, Class D audio power amplifier provides Class AB performance with Class D efficiency. The MAX9773 delivers 1.8W per channel into a  $4\Omega$  load, and offers efficiencies above 90%. Active emissions limiting (AEL) circuitry greatly reduces EMI by actively controlling the output FET gate transitions under all possible transient conditions. AEL controls high-frequency emissions resulting from conventional Class D free-wheeling behavior in the presence of an inductive load. Zerodead-time (ZDT) technology maintains state-of-the-art efficiency and THD+N performance by allowing the output FETs to switch simultaneously without cross conduction. A patented spread-spectrum modulation scheme eliminates the need for output filtering found in traditional Class D devices. These design concepts reduce component count and extend battery life.

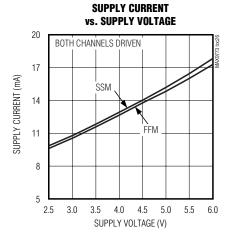

The MAX9773 offers two modulation schemes: a fixedfrequency (FFM) mode, and a spread-spectrum (SSM) mode that reduces EMI-radiated emissions. The MAX9773 oscillator can be synchronized to an external clock through the SYNC input, allowing synchronization of multiple Maxim Class D amplifiers. The sync output (SYNC\_OUT) can be used for a master-slave application where more channels are required. The MAX9773 features a fully differential architecture, a full bridge-tied load (BTL) output, and comprehensive click-and-pop suppression. The device features internally set gains of 12dB, 15.6dB, 20dB, and 26dB selected through two gain-select inputs, further reducing external component count.

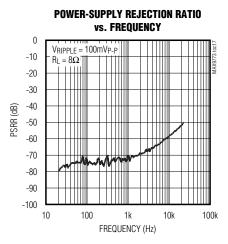

The MAX9773 features high 80dB PSRR, less than 0.1% THD+N, and SNR in excess of 88dB. Short-circuit and thermal-overload protection prevent the device from being damaged during a fault condition. The MAX9773 is available in 24-pin thin QFN-EP (4mm x 4mm x 0.8mm), and 20-bump UCSP™ (2mm x 2.5mm x 0.6mm) packages. The MAX9773 is specified over the extended -40°C to +85°C temperature range.

### **Applications**

Cellular/Multimedia Phones

Notebooks

Handheld Gaming Consoles

MP3 Players

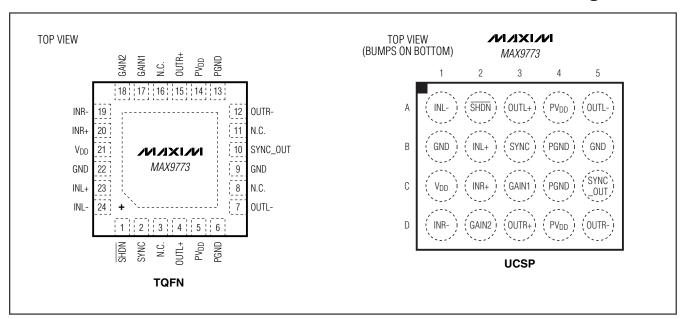

Pin Configurations and Gain Selection appear at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

#### Features

- Filterless Amplifier Passes FCC-Radiation **Emissions Standards with 6in of Cable**

- ♦ Unique Spread-Spectrum Mode and Active **Emissions Limiting Achieves Better than 15dB** Margin Under FCC Limit

- ♦ Zero Dead Time (ZDT) H-Bridge Maintains Good THD+N Performance

- ♦ Single-Supply Operation (2.5V to 5.5V)

- ♦ Stereo Output  $(4\Omega, V_{DD} = 5V, THD+N = 1\%,$ POUT = 1.8W

- ♦ No LC Output Filter Required

- ♦ 85% Efficiency (R<sub>L</sub> =  $8\Omega$ , P<sub>O</sub> = 600mW)

- ♦ Less Than 0.1% THD+N

- ♦ High 80dB PSRR

- **♦ Fully Differential Inputs**

- ♦ Integrated Click-and-Pop Suppression

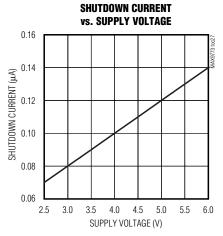

- ♦ Low-Power Shutdown Mode (0.1µA)

- ♦ Short-Circuit and Thermal-Overload Protection

- **♦** Pin-for-Pin Compatible with the MAX9701

- Available in Thermally Efficient, Space-Saving **Packages**

- 24-Pin TQFN-EP (4mm x 4mm x 0.8mm) 20-Bump UCSP (2mm x 2.5mm x 0.6mm)

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|--------------|----------------|-----------------|-------------|

| MAX9773EBP-T | -40°C to +85°C | 20 UCSP-20      | B20-1       |

| MAX9773ETG+  | -40°C to +85°C | 24 TQFN-EP*     | T2444-4     |

<sup>+</sup>Denotes lead-free package.

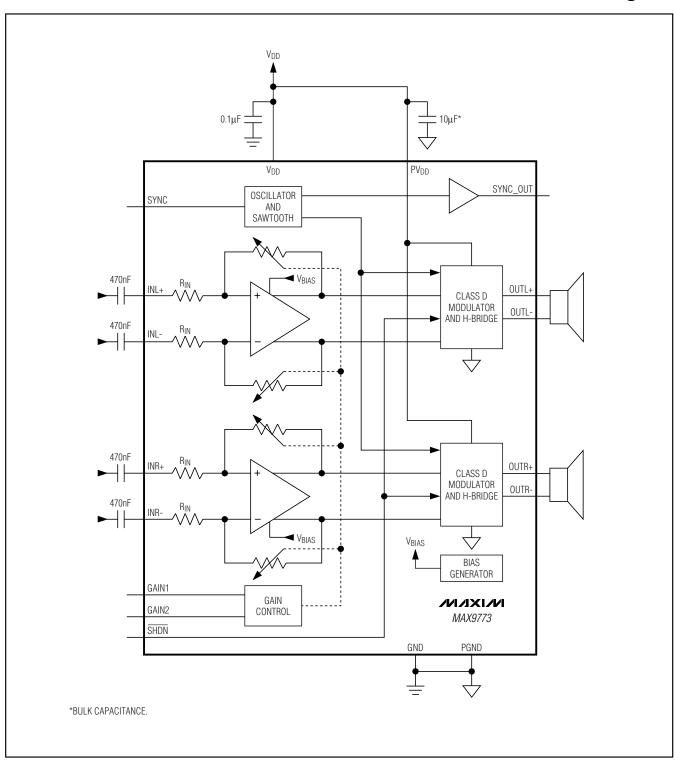

## **Block Diagram**

MIXIM

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                    | 6V                        |

|-------------------------------------------|---------------------------|

| V <sub>DD</sub> to PV <sub>DD</sub>       |                           |

| PV <sub>DD</sub> to PGND                  | 6V                        |

| GND to PGND                               | 0.3V to +0.3V             |

| All Other Pins to GND                     | 0.3V to $(V_{DD} + 0.3V)$ |

| Continuous Current In/Out of PVDD, PGN    | ID, OUT±800mA             |

| Continuous Input Current (all other pins) | ±20mA                     |

| Duration of OUT_Short Circuit to          |                           |

| VDD/GND/PVDD/PGND                         | Continuous                |

| Duration of Short Circuit Between OUT+ and OUTContinuous Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|----------------------------------------------------------------------------------------------------------------|

| 20-Bump UCSP (derate 10mW/°C above +70°C)800mW                                                                 |

| 24-Pin Thin QFN (derate 20.8mW/°C above +70°C)1666.7mW                                                         |

| Junction Temperature+150°C                                                                                     |

| Operating Temperature Range40°C to +85°C                                                                       |

| Storage Temperature Range65°C to +150°C                                                                        |

| Bump Temperature (soldering) Reflow+235°C                                                                      |

| Lead Temperature (soldering, 10s)+300°C                                                                        |

|                                                                                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{PVDD} = V_{\overline{SHDN}} = 3.3V, V_{GND} = V_{PGND} = 0V, SYNC = 0V (FFM), gain = 12dB (GAIN1 = 1, GAIN2 = 1), R<sub>L</sub> connected between OUT+ and OUT-, R<sub>L</sub> = <math>\infty$ , T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                      | SYMBOL            | CONDITIONS                                           |                                          |                 | MIN   | TYP  | MAX   | UNITS  |  |

|--------------------------------|-------------------|------------------------------------------------------|------------------------------------------|-----------------|-------|------|-------|--------|--|

| GENERAL                        |                   |                                                      |                                          |                 |       |      |       |        |  |

| Supply Voltage Range           | V <sub>DD</sub>   | Inferred from PSRR test                              |                                          |                 | 2.6   |      | 5.5   | V      |  |

| Quiescent Current              | I <sub>DD</sub>   | Per channel                                          |                                          |                 |       | 5.5  | 7.5   | mA     |  |

| Shutdown Current               | ISHDN             |                                                      |                                          |                 |       | 0.1  | 10    | μΑ     |  |

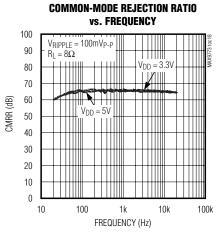

| Common-Mode Rejection Ratio    | CMRR              | $f_{IN} = 1kHz$                                      |                                          |                 |       | 66   |       | dB     |  |

| Input Bias Voltage             | V <sub>BIAS</sub> |                                                      |                                          |                 | 1.125 | 1.25 | 1.375 | V      |  |

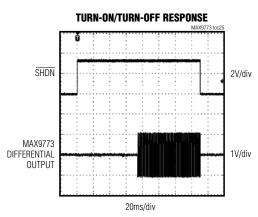

| Turn-On Time                   | ton               |                                                      |                                          |                 |       | 80   |       | ms     |  |

| Output Offset Voltage          | Vos               | $T_A = +25^{\circ}C$                                 |                                          |                 | ±10   | ±50  | mV    |        |  |

|                                |                   | $V_{DD} = 2.5V \text{ to } 5.5V$                     | , V <sub>IN</sub> = 0V, T <sub>A</sub> = | = +25°C         | 59    | 80   |       |        |  |

| Power-Supply Rejection Ratio   | PSRR              | T <sub>MIN</sub> < T <sub>A</sub> < T <sub>MAX</sub> |                                          |                 | 56    |      |       | dB     |  |

| Tower-Supply Rejection Hatto   | 1 31111           | 100mV <sub>P-P</sub> ripple,<br>V <sub>IN</sub> = 0V | f <sub>RIPPLE</sub> = 21                 | 7Hz             |       | 72   |       | ab     |  |

|                                |                   |                                                      | f <sub>RIPPLE</sub> = 20                 | PLE = 20kHz     |       | 50   |       |        |  |

|                                |                   | THD+N = 1%,<br>T <sub>A</sub> = +25°C                | $V_{DD} = 3.3V$ $V_{DD} = 5V$            | $R_L = 8\Omega$ |       | 500  |       |        |  |

|                                | Роит              |                                                      |                                          | $R_L = 4\Omega$ |       | 750  |       | , A/an |  |

| Output Power (Note 3)          |                   |                                                      |                                          | $R_L = 8\Omega$ |       | 1300 |       | mW     |  |

|                                |                   |                                                      | ADD = 2A                                 | $R_L = 4\Omega$ |       | 1800 |       |        |  |

| Total Harmonic Distortion Plus | THD+N             | $R_L = 8\Omega (P_{OUT} = 40)$                       | 00mW), f = 1kH                           | łz              |       | 0.04 |       | %      |  |

| Noise (Note 3)                 | IUD+II            | $R_L = 4\Omega$ ( $P_{OUT} = 60$                     | 00mW), f = 1kH                           | łz              |       | 0.08 |       | /0     |  |

|                                |                   |                                                      | BW = 22Hz                                | FFM             |       | 86   |       |        |  |

| Signal-to-Noise Ratio          | SNR               | Vout = 1V <sub>RMS</sub>                             | to 22kHz                                 | SSM             |       | 86   |       | dB     |  |

| Signal-to-Noise hatto          | SIND              | VOUI = IVRMS                                         | A-weighted                               | FFM             |       | 88.5 |       | ив     |  |

|                                |                   |                                                      | A-weighted                               | SSM             |       | 88.5 |       |        |  |

|                                |                   | SYNC = GND, TA :                                     | = +25°C                                  |                 | 950   | 1100 | 1250  |        |  |

| Oscillator Frequency           | food              | SYNC = unconnect                                     | ted, $T_A = +25^\circ$                   | С               | 1200  | 1400 | 1600  | kHz    |  |

| Oscillator Frequency           | fosc              | SYNC = V <sub>DD</sub> , T <sub>A</sub> =            | - ⊥25°C                                  |                 |       | 1200 |       |        |  |

|                                |                   | OTINO - VDD, TA -                                    | - +20 0                                  |                 |       | ±60  |       |        |  |

| Minimum On-Time                | t <sub>MIN</sub>  |                                                      |                                          |                 |       | 200  |       | ns     |  |

| SYNC Frequency Lock Range      | fsync             |                                                      |                                          |                 | 1000  |      | 2000  | kHz    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{PVDD} = V_{\overline{SHDN}} = 3.3V, V_{GND} = V_{PGND} = 0V, SYNC = 0V (FFM), gain = 12dB (GAIN1 = 1, GAIN2 = 1), R_L connected between OUT+ and OUT-, R_L = <math>\infty$ , T\_A = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T\_A = +25°C.) (Notes 1, 2)

|                                               | PARAMETER SYMBOL CON |                                                                  | •               | MIN | TYP   | MAX       | UNITS |

|-----------------------------------------------|----------------------|------------------------------------------------------------------|-----------------|-----|-------|-----------|-------|

| SYNC_OUT Capacitance Drive                    | Csync_out            |                                                                  |                 | 100 |       | рF        |       |

| Compositive Drive                             | 0                    | Bridge-tied capacitance                                          |                 |     | 200   |           | ي د   |

| Capacitive Drive                              | CL                   | Single ended                                                     |                 |     | 400   |           | pF    |

|                                               |                      | Peak reading, A-weighted,                                        | Into shutdown   |     | -50   |           |       |

| Click-and-Pop Level                           | KCP                  | 32 samples per second (Note 4)                                   | Out of shutdown |     | -50   |           | dBV   |

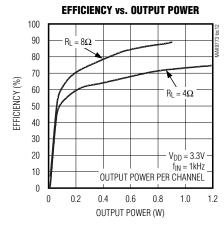

| Efficiency                                    | η                    | $P_{OUT} = 600$ mW per channel $f_{IN} = 1$ kHz, $R_L = 8\Omega$ |                 | 85  |       | %         |       |

|                                               |                      | GAIN1 = 0, GAIN2 = 0                                             |                 | 10  | 16    |           |       |

| Innut Decistores                              | Duri                 | GAIN1 = 1, GAIN2 = 0                                             |                 |     | 30    |           |       |

| Input Resistance                              | HIN                  | GAIN1 = 0, GAIN2 = 1                                             |                 |     | 45    |           | kΩ    |

|                                               |                      | GAIN1 = 1, GAIN2 = 1                                             |                 | 60  |       |           |       |

|                                               |                      | GAIN1 = 0, GAIN2 = 0                                             |                 |     | 26    |           |       |

| Gain                                          | Δ.,                  | GAIN1 = 1, GAIN2 = 0                                             |                 |     | 20    |           | dB    |

| Gaill                                         | Av                   | GAIN1 = 0, GAIN2 = 1                                             | 15.6            |     |       | <u>ub</u> |       |

|                                               |                      | GAIN1 = 1, GAIN2 = 1                                             |                 | 12  |       |           |       |

| Channel-to-Channel Gain<br>Tracking           |                      |                                                                  |                 |     | 1     |           | %     |

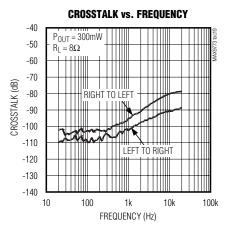

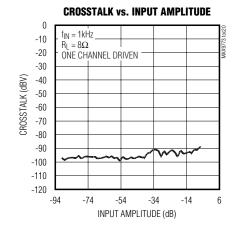

| Crosstalk                                     |                      | L to R, R to L, $f = 10kHz$ , $R_L$<br>$P_{OUT} = 300mW$         | = 8Ω,           |     | 80    |           | dB    |

| DIGITAL INPUTS (SHDN, SYNC                    | , GAIN1, GAIN        | 2)                                                               | •               |     |       |           | •     |

| Input-Voltage High                            | VINH                 |                                                                  |                 | 2   |       |           | V     |

| Input-Voltage Low                             | VINL                 |                                                                  |                 |     |       | 0.8       | V     |

| Input Leakage Current<br>(SHDN, GAIN1, GAIN2) |                      |                                                                  |                 |     |       | ±1        | μΑ    |

| la a de la alea de Compani (OVA)              |                      | V <sub>SYNC</sub> = GND, normal opera                            | ation           | -15 | -7    |           |       |

| Input Leakage Current (SYNC)                  |                      | V <sub>SYNC</sub> = V <sub>DD</sub> , normal opera               | tion            |     | 12 25 |           | μA    |

| DIGITAL OUTPUTS (SYNC_OUT                     | Τ)                   |                                                                  |                 |     |       |           |       |

| Output-Voltage High                           | Voh                  | $I_{OH} = 3mA$ , $V_{DD} = 3.3V$                                 |                 | 2.4 |       |           | V     |

| Output-Voltage Low                            | VoL                  | I <sub>OL</sub> = 3mA                                            |                 |     |       | 0.4       | V     |

- Note 1: All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

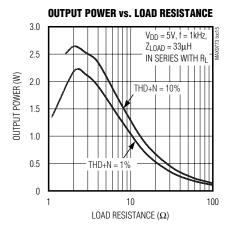

- Note 2: Testing performed with a resistive load in series with an inductor to simulate an actual speaker load. For  $R_L = 4\Omega$ ,  $L = 33\mu H$ . For  $R_L = 8\Omega$ ,  $L = 68\mu H$ .

- Note 3: When driving speakers below  $4\Omega$  with large signals, exercise care to avoid violating the absolute maximum rating for continuous output current.

- Note 4: Testing performed with 8Ω resistive load in series with 68μH inductive load connected across the BTL output. Mode transitions are controlled by SHDN. KCP level is calculated as: 20 x log[(peak voltage during mode transition, no input signal)]. Units are expressed in dBV.

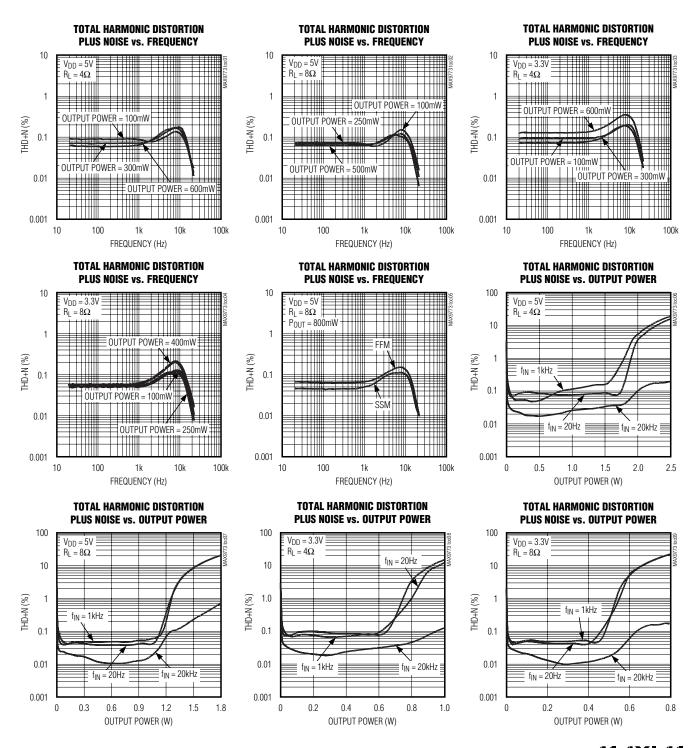

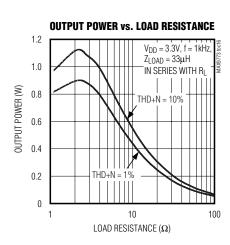

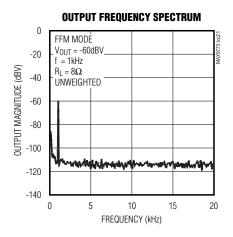

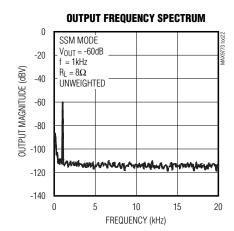

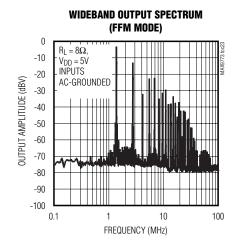

## Typical Operating Characteristics

$(V_{DD} = V_{PVDD} = V_{\overline{SHDN}} = 3.3V, V_{GND} = V_{PGND} = 0V, SYNC = V_{DD} (SSM), gain = 12dB (GAIN1 = 1, GAIN2 = 1)).$

## **Typical Operating Characteristics (continued)**

(VDD = VPVDD = VSHDN = 3.3V, VGND = VPGND = 0V, SYNC = VDD (SSM), gain = 12dB (GAIN1 = 1, GAIN2 = 1)).

## Typical Operating Characteristics (continued)

$(V_{DD} = V_{PVDD} = V_{\overline{SHDN}} = 3.3V, V_{GND} = V_{PGND} = 0V, SYNC = V_{DD} (SSM), gain = 12dB (GAIN1 = 1, GAIN2 = 1)).$

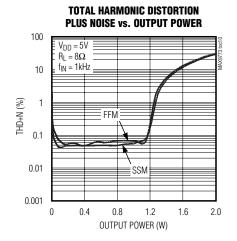

## Typical Operating Characteristics (continued)

(VDD = VPVDD = VSHDN = 3.3V, VGND = VPGND = 0V, SYNC = VDD (SSM), gain = 12dB (GAIN1 = 1, GAIN2 = 1)).

## **Pin Description**

| PI           | PIN    |                  | FUNCTION                                                                                                                                                                                                                                                                                           |

|--------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN         | UCSP   | NAME             | FUNCTION                                                                                                                                                                                                                                                                                           |

| 1            | A2     | SHDN             | Active-Low Shutdown. Connect to V <sub>DD</sub> for normal operation.                                                                                                                                                                                                                              |

| 2            | В3     | SYNC             | Frequency Select and External Clock Input:  SYNC = GND: Fixed-frequency mode with fs = 1100kHz.  SYNC = Unconnected: Fixed-frequency mode with fs = 1400kHz.  SYNC = VDD: Spread-spectrum mode with fs = 1200kHz ±60kHz.  SYNC = Clocked: Fixed-frequency mode with fs = external clock frequency. |

| 3, 8, 11, 16 | _      | N.C.             | No Connection. Not internally connected.                                                                                                                                                                                                                                                           |

| 4            | А3     | OUTL+            | Left-Channel Amplifier Output Positive Phase                                                                                                                                                                                                                                                       |

| 5, 14        | A4, D4 | PV <sub>DD</sub> | H-Bridge Power Supply. Connect to VDD. Bypass with a 0.1µF capacitor to PGND.                                                                                                                                                                                                                      |

| 6, 13        | B4, C4 | PGND             | Power Ground                                                                                                                                                                                                                                                                                       |

| 7            | A5     | OUTL-            | Left-Channel Amplifier Output Negative Phase                                                                                                                                                                                                                                                       |

| 9, 22        | B1, B5 | GND              | Analog Ground                                                                                                                                                                                                                                                                                      |

| 10           | C5     | SYNC_OUT         | Clock Signal Output                                                                                                                                                                                                                                                                                |

| 12           | D5     | OUTR-            | Right-Channel Amplifier Output Negative Phase                                                                                                                                                                                                                                                      |

| 15           | D3     | OUTR+            | Right-Channel Amplifier Output Positive Phase                                                                                                                                                                                                                                                      |

| 17           | C3     | GAIN1            | Gain-Select Input 1                                                                                                                                                                                                                                                                                |

| 18           | D2     | GAIN2            | Gain-Select Input 2                                                                                                                                                                                                                                                                                |

| 19           | D1     | INR-             | Right-Channel Inverting Input                                                                                                                                                                                                                                                                      |

| 20           | C2     | INR+             | Right-Channel Noninverting Input                                                                                                                                                                                                                                                                   |

| 21           | C1     | $V_{DD}$         | Analog Power Supply. Connect to PVDD. Bypass with a 10µF capacitor to GND.                                                                                                                                                                                                                         |

| 23           | B2     | INL+             | Left-Channel Noninverting Input                                                                                                                                                                                                                                                                    |

| 24           | A1     | INL-             | Left-Channel Inverting Input                                                                                                                                                                                                                                                                       |

| EP           | _      | EP               | Exposed Pad. Connect the exposed thermal pad to the GND plane (see the Supply Bypassing, Layout, and Grounding section).                                                                                                                                                                           |

## **Functional Diagram**

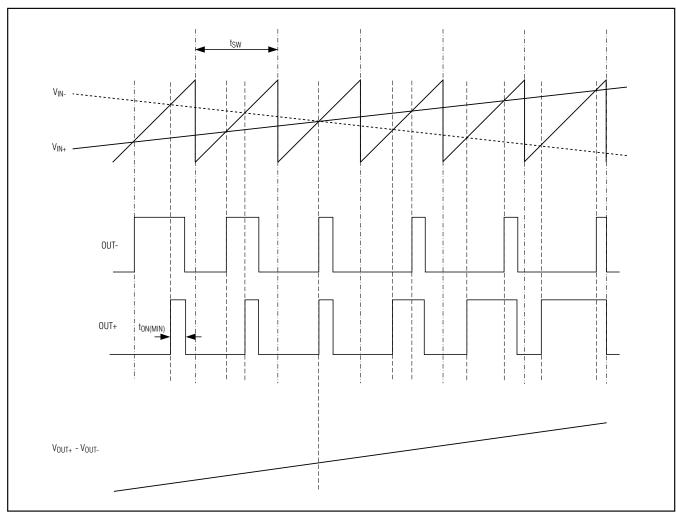

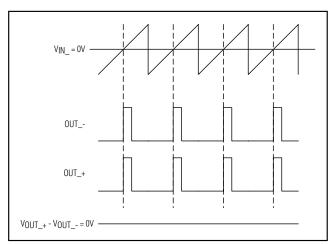

Figure 1. MAX9773 Outputs with an Input Signal Applied

## **Detailed Description**

The MAX9773 ultra-low EMI, filterless, stereo Class D audio power amplifier incorporates several improvements to switch-mode amplifier topology. The MAX9773 features output-driver AEL circuitry to reduce EMI. Zero dead time technology maintains state-of-the art efficiency and THD+N performance by allowing the output FETs to switch simultaneously without cross conduction. The MAX9773 offers Class AB performance with Class D efficiency, while occupying minimal board space. A unique, filterless modulation scheme, synchronizable switching frequency, and spread-spectrum switching mode create a compact, flexible, low-noise, efficient audio power amplifier. The differential input architecture reduces common-mode noise pickup, and can be used without

input-coupling capacitors. The inputs can also be configured to accept a single-ended input signal.

Comparators monitor the MAX9773 inputs and compare the complementary input voltages to the sawtooth waveform. The comparators trip when the input magnitude of the sawtooth exceeds their corresponding input voltage. Both comparators reset at a fixed time after the rising edge of the second comparator trip point, generating a minimum-width pulse (ton(MIN)) at the output of the second comparator (Figure 1). As the input voltage increases or decreases, the duration of the pulse at one output increases while the other output pulse duration remains the same. This causes the net voltage across the speaker (Vout- Vout- to change. The minimum-width pulse helps the device to achieve high levels of linearity.

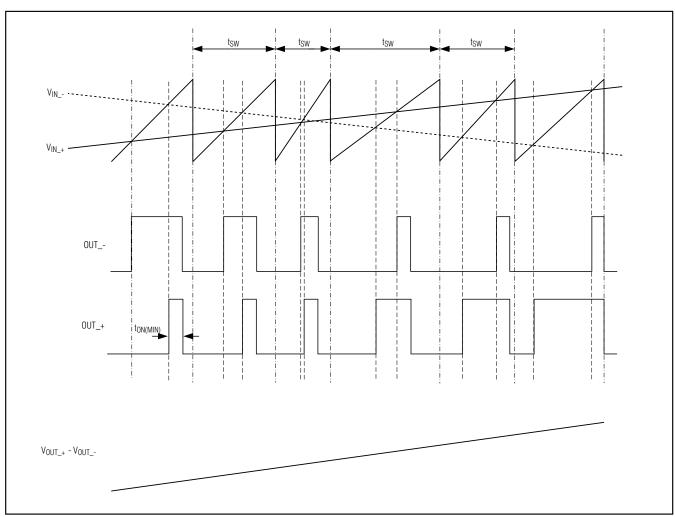

Figure 2. MAX9773 Outputs with an Input Signal Applied (SSM Mode)

# **Operating Modes**Fixed-Frequency (FFM) Mode

The MAX9773 features two fixed-frequency modes. Connect SYNC to GND to select a 1.1MHz switching frequency. Leave SYNC unconnected to select a 1.4MHz switching frequency. The frequency spectrum of the MAX9773 consists of the fundamental switching frequency and its associated harmonics (see the Wideband FFT graph in the *Typical Operating Characteristics*). Program the switching frequency so the harmonics do not fall within a sensitive frequency band (Table 1). Audio reproduction is not affected by changing the switching frequency.

## **Table 1. Operating Modes**

| SYNC            | MODE                                     |

|-----------------|------------------------------------------|

| GND             | FFM with fosc = 1100kHz                  |

| Unconnected     | FFM with fosc = 1400kHz                  |

| V <sub>DD</sub> | SSM with fosc = 1200kHz ±60kHz           |

| Clocked         | FFM with fosc = external clock frequency |

#### Spread-Spectrum (SSM) Mode

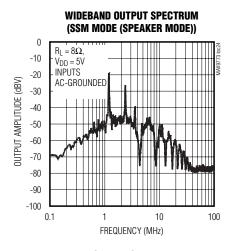

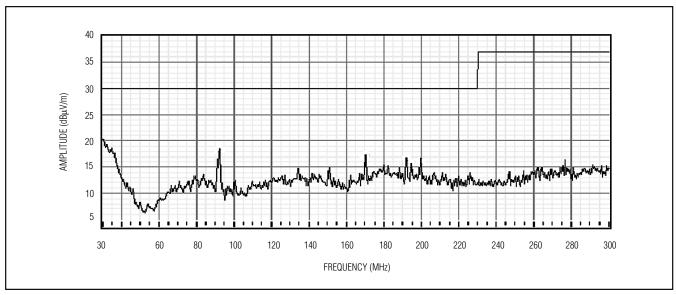

The MAX9773 features a unique, patented spreadspectrum mode that flattens the wideband spectral components, improving EMI emissions that may be radiated by the speaker and cables. This mode is enabled by connecting SYNC to VDD (Table 1). In SSM mode, the switching frequency varies randomly by ±60kHz around the center frequency (1.2MHz). The modulation scheme remains the same, but the period of the sawtooth waveform changes from cycle to cycle (Figure 2). Instead of a large amount of spectral energy present at multiples of the switching frequency, the energy is now spread over a bandwidth that increases with frequency. Above a few megahertz, the wideband spectrum looks like white noise for EMI purposes (Figure 3). A proprietary amplifier topology ensures this does not corrupt the noise floor in the audio bandwidth.

#### Synchronous Switching Mode SYNC

The SYNC input allows the MAX9773 to be synchronized to a user-defined clock, or another Maxim Class D amplifier, creating a fully synchronous system, minimizing clock intermodulation, and allocating spectral components of the switching harmonics to insensitive frequency bands. Applying a TTL clock signal between 1000kHz and 2000kHz to SYNC synchronizes the MAX9773. The period of the SYNC clock can be randomized, allowing

the MAX9773 to be synchronized to another Maxim Class D amplifier operating in SSM mode.

#### SYNC OUT

SYNC\_OUT allows several MAX9773s as well as other Class D amplifiers (such as the MAX9700) to be cascaded. The synchronized output minimizes interference due to clock intermodulation caused by the switching spread between single devices. Using SYNC\_OUT, the modulation scheme remains the same and audio reproduction is not affected by changing the switching frequency.

#### Filterless Modulation/Common-Mode Idle

The MAX9773 uses Maxim's unique, patented modulation scheme that eliminates the LC filter required by traditional Class D amplifiers, improving efficiency, reducing component count, conserving board space and system cost. Conventional Class D amplifiers output a 50% duty cycle, 180° out-of-phase square wave when no signal is present. With no filter, the square wave appears across the load as a DC voltage, resulting in finite load current, which increases power consumption especially when idling. When no signal is present at the input of the MAX9773, the amplifiers output an in-phase square wave as shown in Figure 4. Because the MAX9773 drives the speaker differentially, the two outputs cancel each other, resulting in no net idle mode voltage across the speaker, minimizing power consumption.

Figure 3. EMI Spectrum of MAX9773 with 6in of Twisted-Pair Speaker Cable with TDK Ferrite Beads MPZ1608S300A

Figure 4. MAX9773 Outputs with No Input Signal

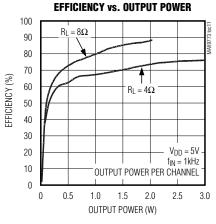

#### **Efficiency**

Efficiency of a Class D amplifier is due to the switching operation of the output stage transistors. In a Class D amplifier, the output transistors act as current-steering switches and consume negligible additional power. Any power loss associated with the Class D output stage is mostly due to the I\*R loss of the MOSFET onresistance, and guiescent-current overhead.

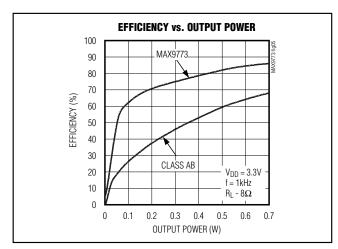

The theoretical best efficiency of a linear amplifier is 78%; however, that efficiency is only exhibited at peak output powers. Under normal operating levels (typical music reproduction levels), efficiency falls below 30%, whereas the MAX9773 still exhibits >80% efficiencies under the same conditions (Figure 5).

#### Shutdown

The MAX9773 has a shutdown mode that reduces power consumption and extends battery life. Driving SHDN low places the MAX9773 in a low-power (0.1 $\mu$ A) shutdown mode. Connect SHDN to V<sub>DD</sub> for normal operation.

#### Click-and-Pop Suppression

The MAX9773 features comprehensive click-and-pop suppression that eliminates audible transients on startup and shutdown. While in shutdown, the H-bridge is in a high-impedance state. During startup, or power-up, the input amplifiers are muted and an internal loop sets the modulator bias voltages to the correct levels, preventing clicks and pops when the H-bridge is subsequently enabled. For 80ms following startup, a soft-start function gradually unmutes the input amplifiers.

## \_Applications Information

#### Filterless Operation

Traditional Class D amplifiers require an output filter to recover the audio signal from the amplifier's PWM output.

Figure 5. MAX9773 Efficiency vs. Class AB Efficiency

The filters add cost, increase the solution size of the amplifier, and can decrease efficiency. The traditional PWM scheme uses large differential output swings (2 x  $V_{DD(P-P)}$ ) and causes large ripple currents. Any parasitic resistance in the filter components results in a loss of power, lowering the efficiency.

The MAX9773 does not require an output filter. The device relies on the inherent inductance of the speaker coil and the natural filtering of both the speaker and the human ear to recover the audio component of the square-wave output. Eliminating the output filter results in a smaller, less costly, more efficient solution.

Because the frequency of the MAX9773 output is well beyond the bandwidth of most speakers, voice coil movement due to the square-wave frequency is very small. Although this movement is small, a speaker not designed to handle the additional power can be damaged. For optimum results, use a speaker with a series inductance >10 $\mu$ H. Typical  $8\Omega$  speakers, for portable audio applications, exhibit series inductances in the range of  $20\mu$ H to  $100\mu$ H.

#### **Output Offset**

Unlike a Class AB amplifier, the output offset voltage of a Class D amplifier does not noticeably increase quiescent current draw when a load is applied. This is due to the power conversion of the Class D amplifier. For example, an 8mV DC offset across an  $8\Omega$  load results in 1mA extra current consumption in a Class AB device. In the Class D case, an 8mV offset into  $8\Omega$  equates to an additional power drain of  $8\mu W$ . Due to the high efficiency of the Class D amplifier, this represents an additional quiescent current draw of:  $8\mu W/(V_{DD}$  / 100 x  $\eta)$ , which is on the order of a few  $\mu A$ .

Table 2. Gain Settings (V<sub>DD</sub> = 3.3V, THD+N = 10%)

| GAIN1 | GAIN2 | GAIN<br>(dB) | INPUT<br>(V <sub>RMS</sub> ) | R <sub>L</sub><br>(Ω) | P <sub>OUT</sub> (mW) |

|-------|-------|--------------|------------------------------|-----------------------|-----------------------|

| 0     | 0     | +26          | 0.097699                     | 4                     | 950                   |

| 1     | 0     | +20          | 0.194936                     | 4                     | 950                   |

| 0     | 1     | +15.6        | 0.323513                     | 4                     | 950                   |

| 1     | 1     | 12           | 0.489657                     | 4                     | 950                   |

| 0     | 0     | +26          | 0.114288                     | 8                     | 650                   |

| 1     | 0     | +20          | 0.228035                     | 8                     | 650                   |

| 0     | 1     | +15.6        | 0.378444                     | 8                     | 650                   |

| 1     | 1     | 12           | 0.572798                     | 8                     | 650                   |

## Table 3. Custom Gain Components

#### Selectable Gain

The MAX9773 features four selectable gain settings, minimizing external component count. Gains of 12dB, 15.6dB, 20dB, and 26dB are set through gain-select inputs, GAIN1 and GAIN2. GAIN1 and GAIN2 can be hardwired or digitally controlled. Table 2 shows the suggested gain settings to attain a maximum output power from a given peak input voltage and given load at  $V_{DD} = 3.3V$  and  $T_{AD} = 10\%$ .

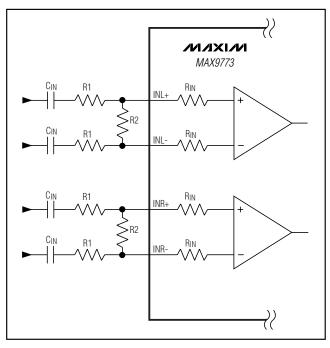

#### **Custom Gain Settings**

The MAX9773 can be set up with any gain setting by adding three external resistors per amplifier. Figure 6 shows the required circuit for setting up custom gain. Table 3 displays a list of the components to use for several gain settings.

| GAIN_S | ETTINGS | CAIN (dD) | <b>D4</b> (O)  | <b>DO</b> (O) | C (115)              | CAIN TOLEDANCE (4D) |

|--------|---------|-----------|----------------|---------------|----------------------|---------------------|

| GAIN1  | GAIN2   | GAIN (dB) | <b>R1 (</b> Ω) | <b>R2</b> (Ω) | C <sub>IN</sub> (μF) | GAIN TOLERANCE (dB) |

| 0      | 0       | 26        | _              | _             | 1                    | _                   |

| 0      | 0       | 25        | 750            | 20k           | 1                    | +0.12/-0.07         |

| 0      | 0       | 24        | 1k             | 10k           | 1.5                  | +0.14/-0.08         |

| 0      | 0       | 23        | 1k             | 6k            | 2.2                  | +0.13/-0.08         |

| 0      | 0       | 22        | 1.5k           | 6k            | 2.2                  | +0.16/-0.1          |

| 0      | 0       | 21        | 2k             | 6k            | 2                    | +0.19/-0.12         |

| 1      | 0       | 20        | _              | _             | 1                    | _                   |

| 1      | 0       | 19        | 1.2k           | 30k           | 1                    | +0.1/-0.06          |

| 1      | 0       | 18        | 2k             | 20k           | 1                    | +0.15/-0.09         |

| 1      | 0       | 17        | 2k             | 10k           | 1.2                  | +0.12/-0.07         |

| 1      | 0       | 16        | 2.5k           | 10k           | 1.2                  | +0.15/-0.09         |

| 0      | 1       | 15        | 1k             | 40k           | 0.86                 | +0.06/-0.03         |

| 0      | 1       | 14        | 2.8k           | 40k           | 0.68                 | +0.15/-0.09         |

| 0      | 1       | 13        | 2.8k           | 20k           | 0.86                 | +0.14/-0.08         |

| 1      | 1       | 12        | _              | _             | 1                    | _                   |

| 1      | 1       | 11        | 1.8k           | 40k           | 0.86                 | +0.08/-0.05         |

| 1      | 1       | 10        | 4k             | 40k           | 0.68                 | +0.15/-0.09         |

| 1      | 1       | 9         | 5k             | 30k           | 0.68                 | +0.17/-0.1          |

| 1      | 1       | 8         | 5k             | 20k           | 0.68                 | +0.15/-0.09         |

| 1      | 1       | 7         | 5.5k           | 16k           | 0.68                 | +0.15/-0.09         |

| 1      | 1       | 6         | 7k             | 16k           | 0.68                 | +0.17/-0.1          |

| 1      | 1       | 5         | 8k             | 14k           | 0.68                 | +0.17/-0.1          |

| 1      | 1       | 4         | 8k             | 12k           | 0.68                 | +0.16/-0.1          |

| 1      | 1       | 3         | 10k            | 12k           | 0.68                 | +0.17/-0.1          |

| 1      | 1       | 2         | 11k            | 10k           | 0.68                 | +0.16/-0.1          |

| 1      | 1       | 1         | 12k            | 10k           | 0.58                 | +0.16/-0.1          |

| 1      | 1       | 0         | 14k            | 10k           | 0.47                 | +0.17/-0.1          |

Figure 6. Custom Gain Setting

The internal input resistance,  $R_{\text{IN}}$ , changes with each gain setting. The R1 resistors attenuate the gain and resistors R2 compensate for  $R_{\text{IN}}$ 's tolerance, which can be as high as 25%.  $C_{\text{IN}}$  must be adjusted to compensate for the total change in input impedance or the low-frequency roll-off point shifts.

# Input Amplifier Differential Input

The MAX9773 features a differential input structure, making it compatible with many CODECs and offers improved noise immunity over a single-ended input amplifier. In devices such as cellular phones, high-frequency signals from the RF transmitter can be picked up by the amplifier's input traces. The signals appear at the amplifier's inputs as common-mode noise. A differential input amplifier amplifies the difference of the two inputs, any signal common to both inputs is canceled.

#### Single-Ended Input

The MAX9773 can be configured as a single-ended input amplifier by capacitively coupling either input to GND, and driving the other input (Figure 7).

### Component Selection Input Filter

An input capacitor, C<sub>IN</sub>, in conjunction with the MAX9773 input impedance (R<sub>IN</sub>) forms a highpass filter that removes the DC bias from an incoming signal. The

Figure 7. Single-Ended Input

AC-coupling capacitor allows the amplifier to automatically bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose  $C_{\text{IN}}$  so  $f_{\text{-}3dB}$  is well below the lowest frequency of interest. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in increased distortion at low frequencies.

Other considerations when designing the input filter include the constraints of the overall system and the actual frequency band of interest. Although high-fidelity audio calls for a flat-gain response between 20Hz and 20kHz, portable voice-reproduction devices such as cellular phones and two-way radios need only concentrate on the frequency range of the spoken human voice (typically 300Hz to 3.5kHz). In addition, speakers used in portable devices typically have a poor response below 300Hz. Taking these two factors into consideration, the input filter may not need to be designed for a 20Hz to 20kHz response, saving both board space and cost due to the use of smaller capacitors.

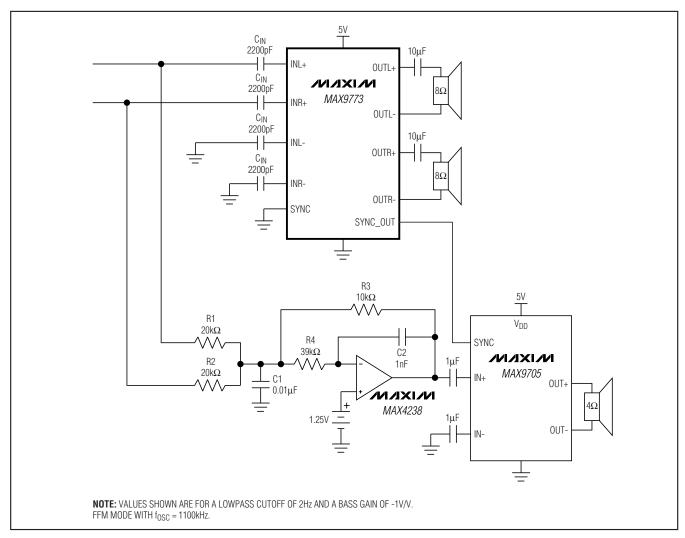

Figure 8. 2.1 Channel Application Circuit

#### **Output Filter**

The MAX9773 does not require an output filter. The device passes FCC emissions standards with 6in of unshielded speaker cables. However, output filtering can be used if a design is failing radiated emissions due to board layout or cable length, or if the circuit is near EMI-sensitive devices. Use a ferrite bead filter when radiated frequencies above 10MHz are of concern. Use an LC filter or a common-mode choke when radiated emissions below 10MHz are of concern, or when long leads (>6in) connect the amplifier to the speaker.

#### 2.1 Channel Configuration

The typical 2.1 channel application circuit (Figure 8) shows the MAX9773 configured as a mid/high-frequency amplifier and the MAX9705 configured as a mono bass amplifier. Input capacitors ( $C_{\rm IN}$ ) set the highpass cutoff frequency according to the following equation:

$$f = \frac{1}{2\pi \times R_{IN} \times C_{IN}}$$

where  $R_{IN}$  is the typical input resistance of the MAX9773. The 10 $\mu$ F capacitors on the output of the MAX9773 ensure a two-pole highpass filter.

Low frequencies are summed through a two-pole lowpass filter and sent to the MAX9705 mono speaker amplifier. The passband gain of the lowpass filter is unity for in-phase stereo signals:

$$A_{VLP} = \frac{-2 \times R3}{R1}$$

where R1 = R2 and R3 = R1//R2. The cutoff frequency of the lowpass filter is set by the following equation:

$$f_{LP} = \frac{1}{2\pi} \times \sqrt{\frac{1}{C1 \times C2 \times R3 \times R4}}$$

#### Supply Bypassing, Layout, and Grounding

Proper layout and grounding are essential for optimum performance. Use large traces for the power-supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance. Large traces also aid in moving heat away from the package. Proper grounding improves audio performance, minimizes crosstalk between channels, and prevents any switching noise from coupling into the audio signal. Connect PGND and GND together at a single point on the PC board. Route all traces that carry switching transients away from GND and the traces/components in the audio signal path.

Bypass V<sub>DD</sub> with a  $0.1\mu F$  capacitor to GND and PV<sub>DD</sub> with a  $10\mu F$  capacitor to PGND. Place the bypass capacitors as close to the MAX9773 as possible. Use large, low-resistance output traces. Current drawn from the outputs increases as load impedance decreases. High-output trace resistance decreases the power delivered to the load. Large output, supply, and GND traces allow more heat to move from the MAX9773 to the air, decreasing the thermal impedance of the circuit.

The MAX9773 thin QFN-EP package features an exposed thermal pad on its underside. This pad lowers the package's thermal impedance by providing a direct heat conduction path from the die to the PC board. Connect the exposed thermal pad to the GND plane.

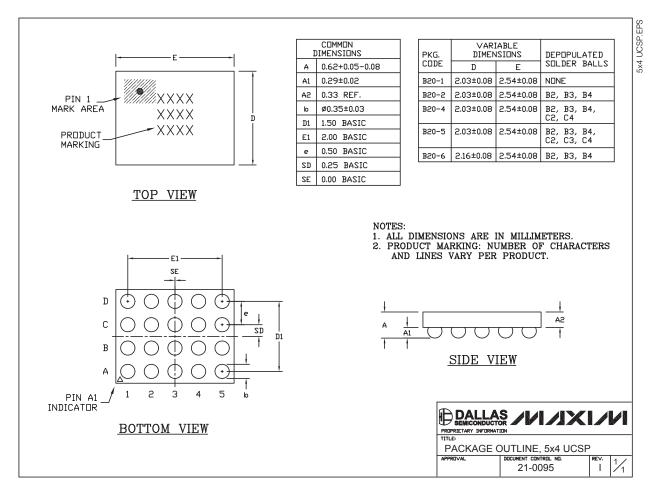

## **UCSP Applications Information**

For the latest application details on UCSP construction, dimensions, tape carrier information, printed circuit board techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to Application Note: UCSP—A Wafer-Level Chip-Scale Package available on Maxim's website at www.maxim-ic.com/ucsp.

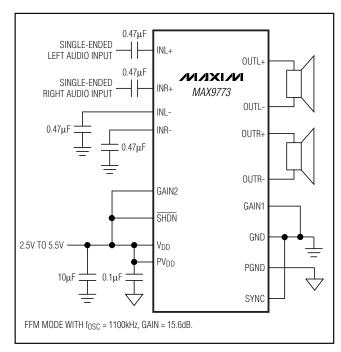

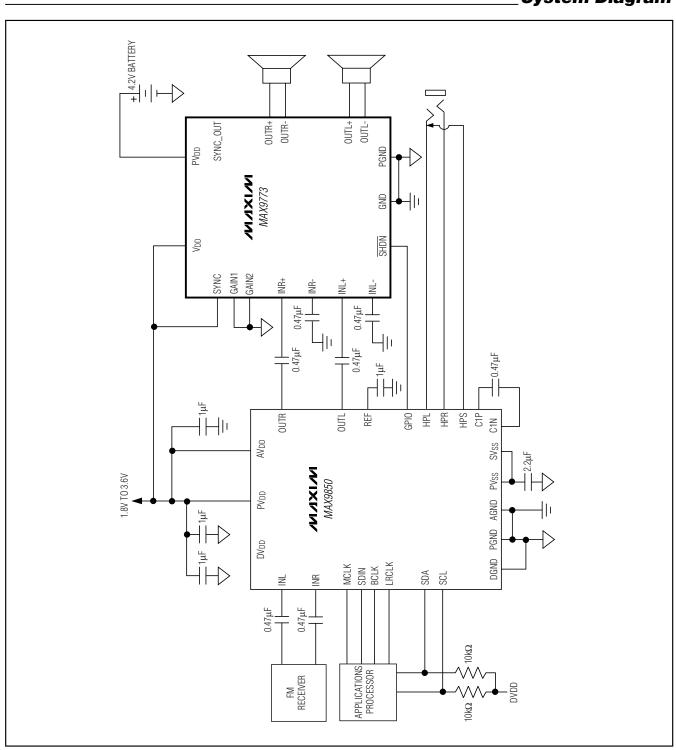

System Diagram

## **Pin Configurations**

#### **Gain Selection**

20

15.6

12

Chip Information

GAIN SELECTION

GAIN (dB)

PROCESS: BICMOS

GAIN1 = 0, GAIN2 = 0

26

GAIN1 = 1, GAIN2 = 0

GAIN1 = 0, GAIN2 = 1

GAIN1 = 1, GAIN2 = 1

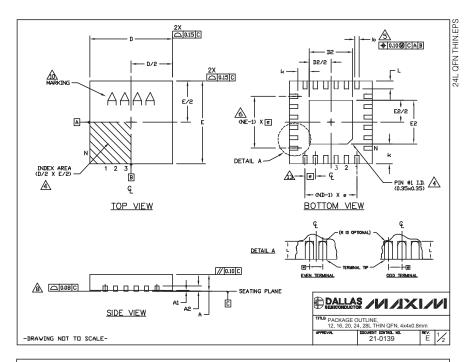

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

| PKG           | 12       | ≥L 4×  | 4    | 16       | L 4x   | 4    | 20        | L 4×  | 4         | 2      | 4L 4× | 4         | 21    | 3L 4× | 4    |

|---------------|----------|--------|------|----------|--------|------|-----------|-------|-----------|--------|-------|-----------|-------|-------|------|

| REF.          | MIN.     | NOM.   | MAX. | MIN.     | NOM.   | MAX. | MIN.      | NDM   | MAX.      | MIN.   | NOM.  | MAX.      | MIN.  | NDM.  | MA)  |

| ٨             | 0.70     | 0.75   | 0.80 | 0.70     | 0.75   | 0.80 | 0.70      | 0.75  | 0.80      | 0.70   | 0.75  | 0.80      | 0.70  | 0.75  | 0.80 |

| A1            | 0.0      | 0.02   | 0.05 | 0.0      | 20.0   | 0.05 | 0.0       | 0.02  | 0.05      | 0.0    | 0.02  | 0.05      | 0.0   | 0.02  | 0.05 |

| A2            | 0.20 REF |        | 0    | 0.20 REF |        |      | 20 RE     | F     | 0         | .20 RE | F     | 0         | 20 RE | F     |      |

| b             | 0.25     | 0.30   | 0.35 | 0.25     | 0.30   | 0.35 | 0.20      | 0.25  | 0.30      | 0.18   | 0.23  | 0.30      | 0.15  | 0.20  | 0.25 |

| D             | 3.90     | 4.00   | 4.10 | 3.90     | 4.00   | 4.10 | 3.90      | 4.00  | 4.10      | 3.90   | 4.00  | 4.10      | 3.90  | 4.00  | 4.10 |

| E             | 3.90     | 4.00   | 4.10 | 3.90     | 4.00   | 4.10 | 3.90      | 4.00  | 4.10      | 3.90   | 4.00  | 4.10      | 3.90  | 4.00  | 4.10 |

| e             |          | .80 BS | C.   | 0.       | .65 BS | C.   | 0.50 BSC. |       | 0.50 BSC. |        |       | 0.40 BSC. |       |       |      |

| k             | 0.25     | -      | -    | 0.25     | -      | -    | 0.25      | ı     | -         | 0.25   | -     | -         | 0.25  | -     | -    |

| L             | 0.45     | 0.55   | 0.65 | 0.45     | 0.55   | 0.65 | 0.45      | 0.55  | 0.65      | 0.30   | 0.40  | 0.50      | 0.30  | 0.40  | 0.50 |

| N             |          | 12     |      |          | 16     |      | 20        |       | 24        |        |       | 28        |       |       |      |

| ND            |          | 3      |      |          | 4      |      |           | 5 6   |           |        | 7     |           |       |       |      |

| NE            |          | 3      |      |          | 4      |      |           | 5     |           | 6      |       |           | 7     |       |      |

| Jedec<br>Var. |          | VGGB   |      |          | WGGC   |      | ,         | √GGD- | 1         |        | WGGD- | 5         | WGGE  |       |      |

| PKG.    |      | 135  |      |      |      | DOWN<br>BONDS |         |

|---------|------|------|------|------|------|---------------|---------|

| CODES   | MIN  | NOM. | MAX. | MIN. | NON. | MAX.          | ALLUVED |

| T1244-3 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | YES     |

| T1244-4 | 1.95 | 2.10 | 2.25 | 1.95 | 5:10 | 2.25          | ND      |

| T1644-3 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | YES     |

| T1644-4 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | NO      |

| T2044-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | YES     |

| T2044-3 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | NO      |

| T2444-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25          | YES     |

| T2444-3 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63          | YES     |

| T2444-4 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63          | NO      |

| T2844-1 | 2.50 | 2.60 | 2.70 | 2.50 | 2.60 | 2.70          | ND      |

EVEREE DAR VARIATIENS

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 DENTFIER AND TERMINAL NUMBERING CONNENTION SHALL CONFORM TO

JESO 95-1 SPP-012, CEDILS OF TERMINAL #1 DENTFIER AND OFFICIAL, BUT MUST BE LOCATED WITHIN

THE ZONE MOLCHED. THE TERMINAL #1 DENTFIER MAY BE DETIMER A MOULD ON WARKED FEATURE.

DIMENSION IS APPLES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm

FROM TERMINAL TP.

- 6 NO AND HE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

DRAWING CONFORMS TO JEDEC MO22O, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- DRAWING CONFORMS TO JEDEC MOZZO, EXLERT FOR LATE

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

COPLANARITY SHALL NOT EXCEED 0.08mm

- WARPAGE SHALL NOT EXCEEND 0.10mm

- \$\frac{1}{\infty}\$ LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY

DALLAS /VI/IXI/VI PACKAGE OUTLINE, 12, 16, 20, 24, 28L THIN QFN, 4x4x0.8mm 21-0139

-DRAWING NOT TO SCALE-

MAX9773 Package Code: T2444-4

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

MAX9773 Package Code: B20-1

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.